Jens Lienig · Manfred Dietrich (Hrsg.)

## Entwurf integrierter 3D-Systeme der Elektronik

Herausgeber

Jens Lienig

Institut für Feinwerktechnik und

Elektronik-Design

TU Dresden

Dresden, Deutschland

Manfred Dietrich Fraunhofer-Institut für Integrierte Schaltungen Institutsteil Entwurfsautomatisierung Dresden, Deutschland

ISBN 978-3-642-30571-9 ISBN 978-3-642-30572-6 (eBook) DOI 10.1007/978-3-642-30572-6

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

#### Springer Vieweg

© Springer-Verlag Berlin Heidelberg 2012

Das Werk einschließlich aller seiner Teile ist urheberrechtlich geschützt. Jede Verwertung, die nicht ausdrücklich vom Urheberrechtsgesetz zugelassen ist, bedarf der vorherigen Zustimmung des Verlags. Das gilt insbesondere für Vervielfältigungen, Bearbeitungen, Übersetzungen, Mikroverfilmungen und die Einspeicherung und Verarbeitung in elektronischen Systemen.

Die Wiedergabe von Gebrauchsnamen, Handelsnamen, Warenbezeichnungen usw. in diesem Werk berechtigt auch ohne besondere Kennzeichnung nicht zu der Annahme, dass solche Namen im Sinne der Warenzeichen- und Markenschutz-Gesetzgebung als frei zu betrachten wären und daher von jedermann benutzt werden dürften.

Gedruckt auf säurefreiem und chlorfrei gebleichtem Papier

Springer Vieweg ist eine Marke von Springer DE. Springer DE ist Teil der Fachverlagsgruppe Springer Science+Business Media www.springer-vieweg.de

#### **Vorwort**

Hochintegrierte Schaltungen mit hunderten Millionen Transistoren sind die Kernstücke fast aller modernen elektronischen Geräte. Dieser bemerkenswerte Fortschritt wurde hauptsächlich durch das Verkleinern der Halbleiterstrukturen erreicht. Die Kosten für jede weitere Strukturverringerung steigen jedoch stark an. Um die Leistung zukünftiger Schaltkreise weiterhin zu erhöhen, gewinnen daher zunehmend neue Technologien und Entwurfsmethoden an Bedeutung.

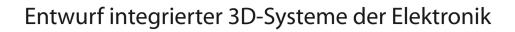

Eine Möglichkeit, den Integrationsgrad von Schaltungen zu steigern, sind dreidimensionale elektronische Systeme (3D-Systeme), bei denen 3D-Integrationstechnologien es erlauben, mehrere Ebenen aktiver Bauelemente übereinander anzuordnen. Das Hinzufügen der dritten Dimension gestattet höhere Integrationsdichten, kürzere Verbindungsleitungen und den Aufbau heterogener Systeme in einer Baugruppe. Der Übergang von zweidimensionalen (2D) zu dreidimensionalen integrierten Systemen (3D) ist auch ein topologischer Wandel, womit der Entwurf dieser Systeme neu auszurichten ist.

Dieses Buch stellt die neuartigen Herausforderungen sowie aktuelle Ergebnisse beim Entwurf von 3D-Systemen vor. Diese beruhen auf Forschungen am Institut für Feinwerktechnik und Elektronik-Design der Technischen Universität Dresden und dem Fraunhofer-Institut für Integrierte Schaltungen/Institutsteil Entwurfsautomatisierung. Die Arbeiten sind zum Teil innerhalb von Förderprojekten des Bundesministeriums für Bildung und Forschung durchgeführt worden. Dies sind die BMBF-Projekte *V3DIM* und *NEEDS* und die EU-Projekte *Therminator* und *e-Brains*, in denen das Fraunhofer-Institut als Partner mitwirkt. Ebenfalls zu nennen ist hier das *Graduiertenkolleg 1401* der DFG, in dessen Rahmen viele der Arbeiten an der TU Dresden erfolgten. Wir danken den Fördergebern für die Möglichkeit, die Forschungen mit ihrer Unterstützung intensiv vorantreiben zu können.

Die Herausgeber möchten sich bei den Autoren für die geleistete Arbeit sowie für ihre wertvollen Beiträge und ihr Engagement bei der Vorbereitung des Buches herzlich bedanken. Damit ist ein Werk entstanden, das einen umfassenden Einblick in die Entwurfsmethoden für die Eroberung der dritten Dimension gibt. Dank gilt auch dem Springer-Verlag, der das schnelle Erscheinen ermöglichte. Die Herausgeber hoffen, dem Leser eine gute Hilfestellung für den Einstieg in die Welt der dreidimensionalen Systemintegration zu geben.

Jens Lienig Technische Universität Dresden Manfred Dietrich Fraunhofer-Gesellschaft

### Inhaltsverzeichnis

| I   | 3D-systeme                                                                                                                               |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1   | Einführung  Jens Lienig und Manfred Dietrich                                                                                             | 3   |

| 2   | <b>Möglichkeiten und Herausforderungen moderner 3D-Systeme.</b>                                                                          | 9   |

| 3   | Layoutrepräsentationen im 3D-Entwurf                                                                                                     | 23  |

| II  | Modellierung und Simulation                                                                                                              |     |

| 4   | Anforderungen an Modellierung und Simulation von 3D-Systemen                                                                             | 55  |

| 5   | <b>3D-Simulation von Strukturen zur Modellgenerierung</b>                                                                                | 65  |

| 6   | Thermische Analyse von 3D-Strukturen                                                                                                     | 89  |

| 7   | XML-basierte Sprache für die hierarchische und parametrisierbare Beschreibung von 3D-Systemen.  Susann Wolf, Andy Heinig und Uwe Knöchel | 107 |

| III | Layoutentwurf                                                                                                                            |     |

| 8   | Herausforderungen bei der Automatisierung des Layoutentwurfs<br>von 3D-Systemen                                                          | 133 |

| 9   | Nutzung von klassischen IP-Blöcken in 3D-Schaltkreisen  Johann Knechtel                                                                  | 145 |

VIII Inhaltsverzeichnis

| 10  | Verdrahtungsvorhersage im dreidimensionalen Layoutentwurf Tilo Meister                | 175 |

|-----|---------------------------------------------------------------------------------------|-----|

| 11  | Thermische Herausforderungen und ihre Berücksichtigung beim 3D-Entwurf Holger Neubert | 191 |

| Glo | ssar                                                                                  | 207 |

| Sac | hverzeichnis                                                                          | 213 |

### Teil I 3D-Systeme

| 1 | Einf | führunş  | g                                                          | 3  |

|---|------|----------|------------------------------------------------------------|----|

| 2 | Möş  | glichkei | ten und Herausforderungen moderner 3D-Systeme              | 9  |

|   | 2.1  | -        | tung                                                       |    |

|   | 2.2  | č        |                                                            | 10 |

|   |      | 2.2.1    | Integration mehrerer Einzelchips (Dies) in einem Gehäuse   |    |

|   |      |          | (MCM und SiP)                                              | 10 |

|   |      | 2.2.2    | Durchkontaktierung von Wafern mittels Through-Silicon Vias | 11 |

|   |      | 2.2.3    | Verbindungstechniken zwischen Dies                         | 12 |

|   |      | 2.2.4    | 3D-Integration durch direktes Stapeln oder mit Interposer  | 13 |

|   | 2.3  | Beispi   | ele für 3D-integrierte Systeme                             |    |

|   |      | 2.3.1    | System-In-Package für Medizintechnik                       |    |

|   |      | 2.3.2    | Anwendungen in der Bildsensorik                            | 15 |

|   |      | 2.3.3    | 3D-Integration von High-End-FPGA                           |    |

|   | 2.4  | Vortei   | lle der 3D-Integration                                     | 17 |

|   |      | 2.4.1    | Kompakte Integration unterschiedlicher IC-Technologien     |    |

|   |      | 2.4.2    | Wiederverwendung existierender integrierter Schaltkreise   | 18 |

|   |      | 2.4.3    | Leistungssteigerung und Reduzierung des Energieverbrauchs  |    |

|   |      |          | durch kürzere Verbindungen                                 |    |

|   |      | 2.4.4    | Schutz des geistigen Eigentums oder sensitiver Daten       |    |

|   | 2.5  | Herau    | sforderungen beim Entwurf                                  |    |

|   |      | 2.5.1    | Vielfalt der Technologievarianten                          |    |

|   |      | 2.5.2    | Multi-physikalische Wechselwirkungen im Stapel             |    |

|   |      | 2.5.3    | Gewährleistung der Energieversorgung im System             |    |

|   |      | 2.5.4    | Fehlende Designkits im Stackingbereich                     |    |

|   |      | 2.5.5    | Sicherstellung der Testbarkeit                             |    |

|   |      | 2.5.6    | Komplexität der Systeme                                    | 21 |

|   | Lite | ratur    |                                                            | 22 |

| 3 | Layo                          | outrepr    | äsentationen im 3D-Entwurf                                              | 23 |

|---|-------------------------------|------------|-------------------------------------------------------------------------|----|

|   | 3.1                           | Einleitung |                                                                         |    |

|   |                               | 3.1.1      | Motivation                                                              | 23 |

|   |                               | 3.1.2      | Definition                                                              | 24 |

|   |                               | 3.1.3      | Abgrenzung                                                              | 25 |

|   |                               | 3.1.4      | Layoutrepräsentationen zur Optimierung im 3D-Entwurf                    | 25 |

|   | 3.2                           | Mode       | rne 3D-Layoutrepräsentationen                                           |    |

|   |                               | 3.2.1      | Klassifikation                                                          | 27 |

|   |                               | 3.2.2      | Mehrlagig dreidimensionale Layoutrepräsentationen                       | 28 |

|   |                               | 3.2.3      | Vollständig dreidimensionale Layoutrepräsentationen                     | 29 |

|   | 3.3                           | Vergle     | eich von 3D-Layoutrepräsentationen                                      | 29 |

|   |                               | 3.3.1      | Laufzeitkomplexität                                                     | 32 |

|   |                               | 3.3.2      | Lösungsraumgröße                                                        | 32 |

|   |                               | 3.3.3      | Klassifizierende Eigenschaften                                          | 32 |

|   |                               | 3.3.4      | Vollständigkeit und Redundanz                                           | 34 |

|   |                               | 3.3.5      | Unterstützte Operationen                                                | 35 |

|   |                               | 3.3.6      | Unterstützte Randbedingungen                                            | 35 |

|   |                               | 3.3.7      | Unterstützung der Kostenbewertung                                       | 35 |

|   | 3.4 Lösungsraumuntersuchungen |            | ngsraumuntersuchungen                                                   | 36 |

|   |                               | 3.4.1      | Methodik                                                                | 36 |

|   |                               | 3.4.2      | Kostenverteilungen                                                      | 37 |

|   |                               | 3.4.3      | Einsatz von Optimierungsverfahren                                       | 41 |

|   | 3.5                           | Schlus     | ssfolgerungen für die Entwicklung von 3D-Layoutrepräsentationen $\dots$ | 42 |

|   | 3.6 3D Moving Block Sequence  |            | oving Block Sequence                                                    | 43 |

|   |                               | 3.6.1      | Orthogonale Blöcke                                                      | 43 |

|   |                               | 3.6.2      | Funktionsweise                                                          | 44 |

|   |                               | 3.6.3      | Experimentelle Ergebnisse                                               | 45 |

|   |                               | 3.6.4      | Ausblick                                                                | 48 |

|   | 3.7                           | Zusan      | nmenfassung                                                             | 48 |

|   | Lites                         | ratur      |                                                                         | 50 |

Einführung 1

#### Jens Lienig und Manfred Dietrich

Die Mikroelektronik ist nach wie vor einer der wichtigsten Treiber von Innovationen. Die gewünschte Qualität und Funktionalität vieler Produkte wird erst durch die Anwendung von Schaltkreisen erreicht. Diese sind für viele Zweige der Industrie der Motor der technischen Entwicklung, und ihr geschickter Einsatz bildet letztlich ein Unterscheidungsmerkmal gegenüber Wettbewerbern. Technische Innovationen, wie das Mobiltelefon und die Play Station, wären ohne die Mikroelektronik undenkbar. Bereits heute lässt sich beispielsweise das Auto als rollendes Mehrprozessorsystem auffassen. Die Realisierung der Sicherheitsfunktionen rund um das Auto und die damit verbundene Senkung der Anzahl der Verkehrstoten bei ständig zunehmendem Verkehr wären ohne die Produkte der Mikroelektronik nicht möglich. Aber auch die Energietechnik, die Medizintechnik und die Automatisierungstechnik profitieren mehr und mehr von dieser Entwicklung. Intelligente elektronische Systeme, gekoppelt mit leistungselektronischen Bauelementen, helfen im Haushalt und in Produktionsanlagen, Energie zu sparen. Der Einsatz regenerativer Energieerzeuger wäre ohne diese Systeme nicht sinnvoll. Neue technische Hilfsmittel in der Medizin ermöglichen komplexere Untersuchungen und neue Therapien. Die minimalinvasive Therapeutik, die von der Kleinheit integrierter Schaltkreise profitiert, erspart dem Patienten Schmerzen und lange Krankenhausaufenthalte. Die Reihe der Aufzählungen ließe sich über die Robotik und Sensornetze beliebig fortsetzen.

Auch in der Zukunft werden neue Anwendungen neuartige Herausforderungen erzeugen. Die Miniaturisierung in der Mikroelektronik schreitet stetig voran und stellt sich damit den Anforderungen zukünftiger Systeme. War bis in das 21. Jahrhundert hinein die

J. Lienig (⊠)

Institut für Feinwerktechnik und Elektronik-Design, Technische Universität Dresden, Dresden, Deutschland

E-Mail: jens.lienig@tu-dresden.de

M. Dietrich

Fraunhofer-Institut für Integrierte Schaltungen, Institutsteil Entwurfsautomatisierung, Dresden, Deutschland

E-mail: manfred.dietrich@eas.iis.fraunhofer.de

4 1 Einführung

Mikroelektronik sehr stark von dem Moore'schen Gesetz geprägt, das aussagt, dass alle 18 Monate sich die Anzahl der Transistoren auf einem Chip verdoppelt, gewinnt in den letzten zwei Jahrzehnten ein zweiter Trend an Bedeutung: Um den Weg der Integration fortzusetzen, ist es erforderlich, ganze Systeme zu integrieren. Die Systeme, also aus einzelnen Komponenten bestehende funktionelle und konstruktive Einheiten, sind jedoch sehr heterogen aufgebaut. Die sie bildenden verschiedenen Komponenten zeichnen sich durch jeweils spezielle Anforderungen an ihre Funktionalität und anderen Eigenschaften aus. Klassischerweise bestehen solche Systeme aus

- Sensoren, welche die Messwerte aus der Umwelt aufnehmen,

- analogen Schaltungen, die die Verbindung zur digitalen Welt der Elektronik herstellen,

- Baugruppen für die digitale Signalverarbeitung und

- Bauelementen der Leistungselektronik, die letztlich Aktoren steuern, welche auf die Umwelt rückwirken.

Aufgrund der sich z. T. widersprechenden Anforderungen an die Komponenten moderner Systeme lassen sich diese nicht mehr in einem Herstellungsprozess, d. h. auf einem Chip, fertigen, da ansonsten zu viele Kompromisse hinsichtlich der Qualität der Einzelkomponenten einzugehen wären. Auch ist eine Ein-Chip-Variante viel zu teuer, die Ausbeute bei der Herstellung würde drastisch sinken und die Zuverlässigkeit der Systeme wäre nicht gewährleistet. Der Einsatz von Leiterplatten, auf denen eine Vielzahl von Einzelschaltkreisen untergebracht werden können, bildet keine Alternative, da trotz beachtlicher Fortschritte in der Leiterplattentechnik deren Größe ein oft unüberwindliches Hindernis ist.

Aus diesem Dilemma heraus wurde nach neuen Ansätzen für die Integration gesucht, die man heute unter dem Begriff "More than Moore" zusammenfasst. "More than Moore" beinhaltet neben der Integration auf dem Chip auch Verfahren zur Integration von mehreren Chips oder anderen elektronischen Bauelementen in möglichst einem Gehäuse. Diese Systemintegration kann über verschiedene Wege beschritten werden. Die einfachste und vielfach schon genutzte Technologie ist die sogenannte System-in-Package-Integration. Dabei werden mehrere Chips und eventuell passive und aktive Einzelbauelemente auf einem Interposer, einer isolierenden Zwischenschicht mit eingebetteten Leiterzügen, platziert. Diese Chips lassen sich dann mittels Leitbahnen auf dem Interposer elektrisch kontaktieren. Die so verbundenen Chips werden abschließend in einem Gehäuse untergebracht, so dass eine kompakte Komponente entsteht, die ein ganzes System enthält. Der Vorteil dieser Methode besteht darin, dass Chips aus verschiedenen Herstellungstechnologien auf engstem Raum miteinander verbunden sind. Außerdem lassen sich andere Verbindungstechniken, wie z. B. optische Leiter, zwischen den Chips nutzen. Aber auch dieser zweidimensionalen Integration sind klare Grenzen gesetzt:

- Die Anzahl der integrierbaren Chips ist aufgrund der zunehmenden notwendigen Fläche für die Unterbringung der Einzelchips begrenzt.

- Die Anzahl der Anschlüsse zwischen den Chips ist limitiert (die Parallelität der Signalübertragung ist eingeschränkt).

1 Einführung 5

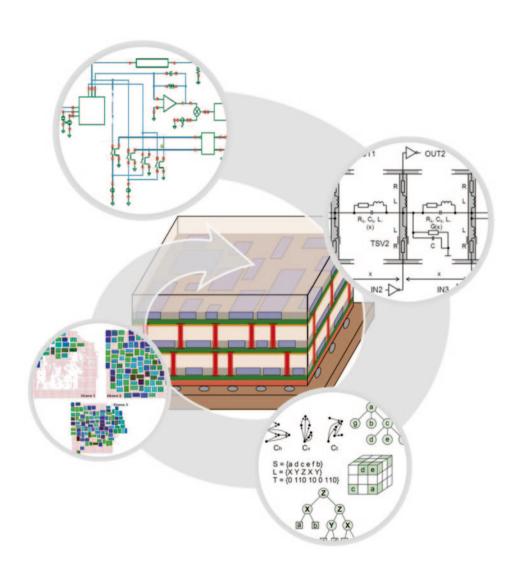

**Abb. 1.1** Das Spektrum moderner 3D-Systeme reicht von 3D-Baugruppen, bestehend aus unabhängig voneinander hergestellten Chips (*links*), bis hin zu 3D-Schaltkreisen, die sich durch Wafer-Integration herstellen lassen (*rechts*). Während 3D-Baugruppen die vertikale Integration verschiedener heterogener Technologien fördern (z. B. System-in-Package), ermöglichen 3D-Schaltkreise dichter gepackte Bauelemente aufgrund kürzerer Vertikalabstände

• Die relativ langen Leitungen erzeugen große parasitäre Effekte und erfordern höhere Energien zur Signalübertragung.

Unter Einbeziehung der dritten Dimension in die Systemintegration lassen sich diese Nachteile überwinden. Die Nutzung der dritten Dimension wird beispielsweise durch 3D-Baugruppen (Abb. 1.1, links) und 3D-Schaltkreise (Abb. 1.1, rechts) möglich. Dabei werden die einzelnen Schaltkreislagen übereinander angeordnet, z. B. auf Chipebene (3D-Baugruppen) oder auf Waferebene (3D-Schaltkreise). Um die nun mehrfach vorhandenen Schaltkreislagen elektrisch leitend zu verbinden, sind sogenannte Through-Silicon Vias (TSVs) zu erzeugen. Dazu ätzt man Löcher in die Wafer. Diese Löcher werden dann mit metallischen Substanzen gefüllt, so dass eine leitende Verbindung zwischen den einzelnen Schaltkreislagen entsteht.

Begrenzt werden die Möglichkeiten zur 3D-Integration durch mechanische Festigkeitsprobleme, durch das Herstellungsverfahren (je mehr gestapelte Wafer, desto höher ist die Wahrscheinlichkeit für Fehler in der Fertigung) und insbesondere durch den thermischen Energieumsatz innerhalb des Stapels. Die auftretenden Verlustleistungen führen zur Erwärmung des Stapels, wobei höhere Temperaturen sich negativ auf die Zuverlässigkeit der Bauelemente auswirken. Die damit notwendige Wärmeabfuhr ist jedoch aus den inneren Wafern heraus nur eingeschränkt möglich. Eine optimierte Stapelung der Wafer und das Verwenden zusätzlicher Wärmeabfuhrmechanismen sind daher bei komplexen 3D-Systemen unabdingbar. Eine weitere Grenze ist die Sicherung der Testbarkeit des Stapels. Nach der Herstellung muss die vollständige Prüfung und eventuell eine Fehlerdiagnose möglich sein. Dies ist eine besondere Herausforderung, da der Stapel oftmals aus verschiedenartigen Chips besteht.

Diesen Grenzen bzw. Herausforderungen bei der 3D-Integration stehen jedoch eine Reihe von Vorteilen gegenüber:

- Die hohe Integrationsdichte pro Volumeneinheit,

- die hohe Parallelität (theoretisch sind bis zu einigen tausend Durchkontaktierungen zwischen zwei Ebenen möglich),

- die kurzen Leitungswege, die zu einer Verringerung der Treiberleistungen führen,

6 1 Einführung

• die Wiederverwendbarkeit von Standardschaltkreisen zur Kostensenkung (z. B. Speicher),

- die mögliche Partitionierung in mehrere kleine Chips statt eines großen (erhöht die Ausbeute),

- die Verwendung von mehreren preiswerten Technologien, die auch von verschiedenen Herstellern stammen können, statt einer sehr teuren (kleine Chips sind sehr homogen und benötigen nur wenige Herstellungsschritte).

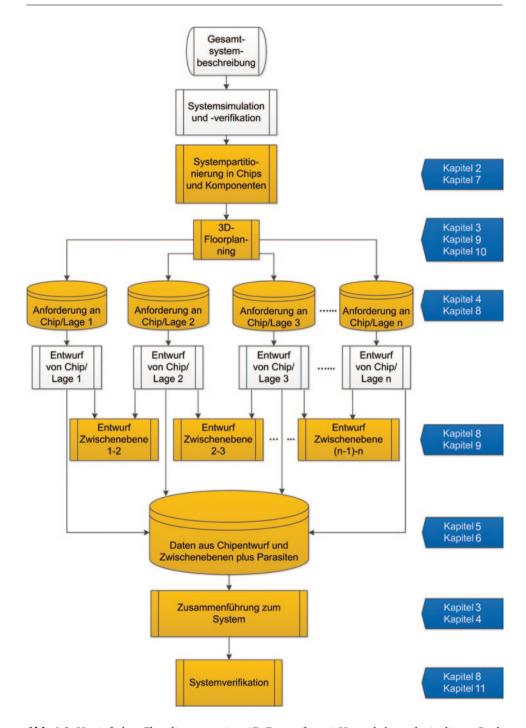

Aufgrund der Komplexität der sich aus der 3D-Integration ergebenden neuartigen 3D-Systeme ist deren Entwurfsfluss, also die Schrittfolge ihrer Entwicklung, grundlegend zu überarbeiten. Neben dem Entwurf des Gesamtsystems schließt dieser 3D-Designflow auch den Entwurf von Einzelchips ein, sind diese doch nun als integrale Systembestandteile mit speziellen Anforderungen, wie z. B. deren Kontaktierung, zu entwickeln. Außerdem ist eine Vielzahl von neuen, zusätzlichen Aktivitäten erforderlich, auf die nachfolgend eingegangen wird.

Besondere Anforderungen ergeben sich bereits bei der Definition des Gesamtsystems, das weit mehr Komponenten enthält als bisherige System-on-Chip-Systeme. Auch besitzt es eine größere Vielfalt von Komponenten. Dieses System ist zu simulieren und zu verifizieren. Nachdem die Fehlerfreiheit des Gesamtsystems festgestellt worden ist, muss man dieses mittels einer zielgerichteten Planung bezüglich der geometrischen Anordnung und Stapelung partitionieren. Bei der Partitionierung ist bereits darauf zu achten, dass eine sinnvolle Platzierung von Komponenten auf den Einzelchips erfolgen kann. Hierbei sind die Zieltechnologie für den jeweiligen Chip, die Testbarkeit, Wärmeverhältnisse und Timing-Anforderungen zu berücksichtigen. Der Partitionierung schließt sich das 3D-Floorplanning an, bei dem die grobe Anordnung von Komponenten auf den Einzelchips, einschließlich der Platzierung der erforderlichen Durchkontaktierungen, erfolgt.

Die Partitionierung und das Floorplanning liefern auch die Daten für den Einstieg in den konventionellen 2D-Entwurf der einzelnen Chips. Dabei sind neben der funktionellen Sicherstellung auch die Kosten der Fertigung in die Betrachtung einzubeziehen. Außerdem ist zu beachten, dass die Testfähigkeit sowohl der einzelnen Chips als auch des gesamten Stapels erhalten bleibt.

Aus diesen einführenden Bemerkungen erkennt man, dass im Rahmen von 3D-Systemen eine Vielzahl neuer Entwurfsaktivitäten notwendig werden. Auch sind die bisherigen Schritte beim konventionellen 2D-Design an die speziellen Erfordernisse für den 3D-Entwurf anzupassen bzw. zu erweitern. Dieses Buch stellt die sich damit ergebenden neuartigen Herausforderungen beim Entwurf von 3D-Systemen vor. Es soll Entwerfern helfen, sich mit der Problematik der dritten Dimension auseinanderzusetzen und erste Eindrücke vom Herangehen an den Entwurf zu gewinnen. Außerdem soll es anregen, sich intensiv mit den Möglichkeiten der 3D-Integration auseinanderzusetzen und auch eigene Forschungen auf diesem Gebiet zu starten oder auszubauen. Die einzelnen Teile sind so gestaltet, dass der Leser sich auf bestimmte, für ihn wichtige Aspekte konzentrieren kann. Dies sind insbesondere die Modellierung von technologienahen neuen Aspekten und ein durchgängiges Konzept zum Layoutentwurf.

Um den Umfang des Buches nicht zu sprengen, wurde bewusst auf die Darstellung bestimmter Entwurfsaktivitäten verzichtet (Abb. 1.2). Dies betrifft die Schritte, die vom

1 Einführung 7

**Abb. 1.2** Vereinfachtes Flussdiagramm eines 3D-Entwurfes, mit Hervorhebung der in diesem Buch beschriebenen Schritte

8 1 Einführung

konventionellen 2D-Entwurf beibehalten werden, wie z. B. die Platzierung und die Verdrahtung von Standardzellen.

Der erste Teil des Buches gibt eine Übersicht zu den Möglichkeiten und Herausforderungen des 3D-Entwurfs. Er erläutert anhand von Beispielen, wie ein Übergang von der 2D-Integration zur 3D-Integration gemeistert werden kann. Außerdem wird eine kurze Einführung zu vorhandenen und neu entwickelten Entwurfsverfahren gegeben. Auch erhält der Leser eine kurze Übersicht über die technologischen Möglichkeiten und Varianten der 3D-Integration. Dabei wird anhand der Herstellungsverfahren das Verständnis vermittelt, wie bei einer Entscheidungsfindung zur Auswahl einer 3D-Integrationsvariante vorzugehen ist.

Im zweiten Teil werden Anforderungen an die Modellierung von neuartigen 3D-Systemen beschrieben. Dazu geben die einzelnen Kapitel einen Einblick in die Anwendung von 3D-Analysen und -Simulationen für die Modellgenerierung zur Simulation eines Gesamtsystems. Die Autoren zeigen Wege auf, wie man elektromagnetische und thermische Einflüsse bestimmt und, ausgehend von diesen Analysen, mittels moderner Modellierungsmethoden zu anwendungsgerechten und vereinfachten Modellen kommt. Dabei wird u. a. das elektrische Verhalten der Verbindungsstrukturen untersucht. Ebenfalls zu betrachten sind die thermischen Eigenschaften eines 3D-Stapels. Dabei spielt einerseits die thermische Interaktion zwischen den Stapeln und andererseits die Wärmeabfuhr aus dem Stapel eine wichtige Rolle. Es werden Analysemöglichkeiten vorgestellt und Vorschläge für die Lösung der thermischen Probleme aufgezeigt. Das letzte Kapitel im zweiten Teil stellt einen neuen Ansatz für die Beschreibung von geometrischen 3D-Strukturen vor, da bei diesen angepasste Beschreibungssprachen bisher fehlen. Mittels der Sprache XML wird ein Beschreibungskonzept entwickelt, das flexibel den Anforderungen von 3D-Systemen gewachsen ist.

Im dritten Teil wenden sich die Autoren dem Layoutentwurf zu. Hier sind einschneidende Maßnahmen erforderlich, um den Anforderungen der dritten Dimension gerecht zu werden. Das erste Kapitel im dritten Teil (Kap. 8) erläutert detailliert die sich aus der 3D-Integration ergebenden wesentlichen Herausforderungen und zeigt neuartige Lösungsansätze auf. Die nachfolgenden Kapitel dieses Teils gehen auf die 3D-spezifischen Anforderungen bei der Layoutgenerierung vertiefend ein. Beginnend mit der weiteren Nutzung von klassischen IP-Blöcken auch in 3D-Systemen sowie einem Ansatz für die 3D-Verdrahtungsvorhersage bis hin zu thermischen Lösungsansätzen wird der Bogen gespannt.

Ein Glossar mit wichtigen Fachbegriffen des 3D-Entwurfs schließt das Buch ab.

# Möglichkeiten und Herausforderungen moderner 3D-Systeme

Uwe Knöchel

#### 2.1 Einleitung

Funktionsumfang, Größe und Preis eines Smartphones veranschaulichen die technologische Entwicklung, die in der Mikroelektronik in den vergangenen Jahren stattgefunden hat. Grundlage dafür war vor allem die System-on-Chip (SoC) Technologie, die es erlaubte, immer mehr Funktionen in einer einzelnen integrierten Schaltung zu realisieren. Durch die gleichzeitige Verkleinerung der Prozessstrukturen konnte die Fläche eines Schaltkreises trotz steigender Transistorzahlen konstant gehalten werden. Mit aktuellen Halbleitertechnologien ist das Potenzial der Strukturverkleinerung weitgehend ausgeschöpft. Besonders analoge Schaltungen, die in modernen Systemen zur Ansteuerung von Sensoren und zur Kommunikation mit der Umgebung benötigt werden, lassen sich nicht weiter verkleinern. Deshalb wird neben dem SoC seit einigen Jahren ein alternativer Integrationsansatz entwickelt, der es ermöglicht, mehrere integrierte Schaltkreise (ICs) in einem gemeinsamen Gehäuse zu integrieren. Auf diese Weise lassen sich verschiedene Halbleitertechnologien auf engstem Raum zu einem System zusammenfügen. Das ist besonders vorteilhaft, wenn ein System sehr unterschiedliche Funktionen erfüllen muss, oder wenn es aufgrund seiner Komplexität nicht mehr wirtschaftlich als IC gefertigt werden kann.

Heute existieren verschiedene 3D-Integrationstechnologien, die sich hinsichtlich ihrer technologischen Reife und Leistungsfähigkeit unterscheiden. Neben der Beherrschung der Fertigungstechnologie stellt der Entwurf dieser Systeme eine große Herausforderung dar. Ohne die Neu- und Weiterentwicklung von Entwurfsverfahren und -werkzeugen können die Vorteile der 3D-integrierten Systeme nicht ausgeschöpft werden.

Fraunhofer-Institut für Integrierte Schaltungen, Institutsteil Entwurfsautomatisierung, Dresden, Deutschland

U. Knöchel (⊠)

E-Mail: uwe.knoechel@eas.iis.fraunhofer.de

#### 2.2 Evolution vom integrierten Schaltkreis (IC) zum 3D-System

Wie keine andere Branche hat die Mikroelektronik die Leistungsfähigkeit ihrer Systeme vervielfacht, ohne dabei mehr Materialien und Energie zu verbrauchen.

Bei diskreten Bauelementen entfällt ein größerer Teil des Volumens auf Gehäuse und Anschlussdrähte. Es war naheliegend, diese Bauelemente auf einem gemeinsamen Siliziumchip anzuordnen, entsprechend der gewünschten Funktion zu verbinden und zu fertigen. Erste integrierte Schaltungen (ICs) umfassten nur wenige Logiktransistoren. Mit fortschreitender Miniaturisierung werden heute ganze Systeme auf einem Chip gefertigt. Man bezeichnet diese als *System-On-Chip* (SoC). Vertreter sind zum Beispiel moderne Mikrokontroller, die das Herzstück vieler Anwendungen sind. Sie vereinen einen Prozessor, Speicher und Analog-Digital- und Digital-Analog-Wandler, die das Auswerten von Sensordaten oder die Steuerung von Prozessen erlauben.

Die Integration analoger und digitaler Schaltungen in einem gemeinsamen Halbleiterprozess ist eine große Herausforderung im Entwurf. Während für Digitalschaltungen immer kleinere Strukturbreiten zur Anwendung kommen, lassen sich analoge Schaltungen kaum skalieren, da hier die Transistordimensionen den zu treibenden Strömen angepasst werden müssen. Die Integration verschiedenartiger Teilsysteme erfordert deshalb oft Kompromisse hinsichtlich Leistungsfähigkeit, Energieverbrauch und Entwurfs- sowie Herstellungskosten. Moderne Integrationsverfahren, die verschiedene ICs in einem Gehäuse vereinen, schließen diese Lücke.

## 2.2.1 Integration mehrerer Einzelchips (Dies) in einem Gehäuse (MCM und SiP)

Die Idee, mehrere Dies in einem Gehäuse anzuordnen, ist nicht neu. Bereits in den 70er Jahren wurden einzelne ICs in einem gemeinsamen Gehäuse, dem *Multi-Chip-Modul* (MCM) integriert. Ein Stapeln von Chips erfolgt dabei nicht. Im einfachsten Fall werden alle Anschlüsse der ICs nach außen geführt. Die Zusammenfassung der Chips im Modul bringt funktionell kaum Vorteile, vereinfacht aber die Fertigung der Leiterplatte, da weniger Bauteile zu bestücken sind.

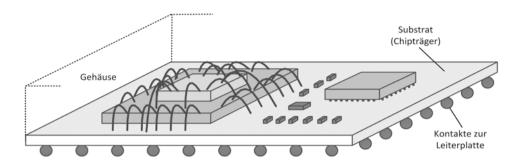

Werden zusätzlich passive Bauelemente, Sensoren oder spezielle Interface-Schaltkreise verbaut, spricht man vom *System-In-Package* (SiP) [Tum06]. Im Unterschied zum MCM werden Schaltkreise und passive Bauelemente über das Substrat des SiP untereinander verschaltet. Nur die für die Verbindung zur Peripherie erforderlichen Anschlüsse werden nach außen geführt. Als Substrate kommen meist dünne Laminate zum Einsatz, die zwei bis vier Verdrahtungsebenen besitzen. Die ICs werden auf das Substrat geklebt und gebondet oder in Flip-Chip-Technik verlötet. Mit geeigneten Klebe- und Bondtechniken lassen sich außerdem wenige ICs übereinander stapeln. Die Platzierung nebeneinander überwiegt jedoch. Zusätzlich zu den ICs können passive Bauelemente in SMD-Form im SiP untergebracht werden. Dazu zählen beispielsweise Stützkondensatoren oder Oszillato-

Abb. 2.1 Aufbau eines System-In-Package (SiP)

ren, die sich monolithisch auf einem IC schlecht integrieren lassen, jedoch als Standardbauelemente kostengünstig verfügbar sind. Abbildung 2.1 zeigt den prinzipiellen Aufbau eines SiP.

Wenn beim Entwurf der SiP auf existierende und erprobte Einzelschaltkreise zurückgegriffen werden kann, lassen sich auf diese Weise komplexe Systeme verhältnismäßig schnell entwerfen und auf den Markt bringen. Die Möglichkeit, Teilsysteme unterschiedlicher Halbleitertechnologien miteinander zu kombinieren, ist ein großer Vorteil gegenüber monolithisch integrierten SoC.

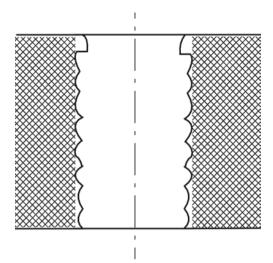

#### 2.2.2 Durchkontaktierung von Wafern mittels Through-Silicon Vias

Die Entwicklung der Durchkontaktierung von Silizium-Dies, *Through-Silicon Vias* (TSVs) genannt, ist die entscheidende Voraussetzung für das Stapeln von integrierten Schaltkreisen. Die TSVs sind elektrisch leitende Durchkontaktierung durch den Substratwerkstoff zur Verbindung mehrerer Schaltkreislagen.

Die Verdrahtung der Bauelemente eines einzelnen ICs und der Kontakt zu Bonddrähten oder Lötkugeln (Pads) erfolgt in den Metallisierungsebenen oberhalb der aktiven Halbleiterschichten. Um ein Stapeln zu ermöglichen, müssen die Kontaktflächen durch die Siliziumschicht an die Unterseite des ICs gebracht werden. Dazu sind Löcher in das Silizium einzubringen, die mit leitfähigem Kupfer oder Wolfram gefüllt werden. Die Herstellung dieser Durchkontaktierung kann vor (*Via-First-TSV*), zwischen und nach den herkömmlichen Prozessschritten (*Via-Last-TSV*) erfolgen. Beim nachträglichen Prozessieren der Vias lässt sich der einzelne IC bei einem beliebigen Halbleiterhersteller fertigen.

Die Herstellung der TSVs erfolgt heute überwiegend durch reaktives Ionentiefenätzen, auch Bosch-Prozess genannt, der aus wiederholten Ätz- und Passivierungsvorgängen besteht [Tum10]. Da das Ätzmittel nicht nur in die Tiefe, sondern auch an den Rändern des zu fertigenden TSV wirkt, kann dieser nicht in einem Schritt geätzt werden. Nach einer bestimmten Ätztiefe muss zunächst eine Passivierung der Seitenwand erfolgen, um das geforderte Aspektverhältnis aus TSV-Tiefe und -Durchmesser zu erreichen.

Die Anzahl der Zyklen im Boschprozess beeinflusst die Rauigkeit der TSV-Seitenwand und das Verhältnis von Durchmesser und Tiefe (Abb. 2.2). Eine hohe Zyklusanzahl verbessert die Eigenschaften des TSV, verursacht jedoch höhere Herstellungskosten.

Die Eigenschaften gegenwärtiger TSV-Technologien sind:

- Durchmesser: d=(5...20) μm, Durchmesser Kupfer-TSV bis 100 μm

- Aspektverhältnis Durchmesser/Tiefe: bis 1/10

- Isolation: SiO<sub>2</sub> 0,4 μm

- Mindestmittenabstand benachbarter TSVs: 3-4facher Durchmesser

Aufgrund des begrenzten Aspektverhältnisses werden die durchzukontaktierenden Wafer auf 20 bis  $100~\mu m$  Dicke gedünnt. Neben der elektrischen Leitfähigkeit unterstützen TSVs die Wärmeableitung (s. Kap. 11).

#### 2.2.3 Verbindungstechniken zwischen Dies

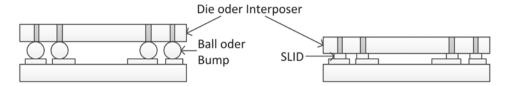

Nachdem die Dies übereinander positioniert wurden, erfolgt ihre elektrische und mechanische Verbindung durch Druck und Wärme. Eine Möglichkeit ist das Aufbringen sehr kleiner Lötkugeln, die als Balls oder Bumps bezeichnet werden. Das Verbinden mit der solid-liquid interdiffusion (SLID) Technik hingegen benötigt flache Kontaktflächen. Abbildung 2.3 veranschaulicht beide Verbindungstechniken.

Insbesondere wenn mehrere Dies nacheinander gestapelt und verlötet werden, ist zu beachten, dass diese Kontakte ihre Form und Eigenschaften bei mehrmaligem Erwärmen verändern. Die Größe der Kontaktflächen bestimmt die erforderliche Positioniergenauig-

**Abb. 2.3** Verbindungstechniken zwischen Dies durch Lötkugeln (*links*) oder Solid-liquid Interdiffusion (SLID) *rechts*

**Tab. 2.1** Größen von Verbindungselementen zwischen Dies

|                     | Ball/Bump | Mikroball | SLID |

|---------------------|-----------|-----------|------|

| Minimale Größe (μm) | 200       | 50        | 30   |

| Maximale Größe (µm) | 500       | 200       | 200  |

keit und hat damit Einfluss auf die Fertigungskosten. Tabelle 2.1 zeigt die Eigenschaften dieser Elemente. Der Mindestabstand zwischen zwei benachbarten Kontaktierungen entspricht deren doppelten Durchmesser.

#### 2.2.4 3D-Integration durch direktes Stapeln oder mit Interposer

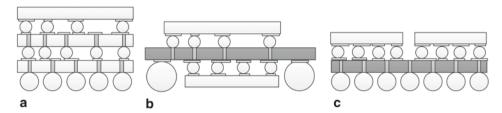

Beim direkten Stapeln von ICs ist es unerlässlich, dass sich die Kontaktflächen des unteren ICs exakt an den Positionen befinden, an dem der obere IC angeschlossen wird. Dabei müssen nicht nur Signalleitungen, sondern auch Stromversorgungsanschlüsse bereitgestellt werden. Das bedeutet, dass beide ICs nicht nur hinsichtlich ihrer Funktion, sondern auch in der Platzierung ihrer Baugruppen (Layout) aufeinander abgestimmt sind. Abbildung 2.4a zeigt die direkte Stapelung. Mit Ausnahme des obersten ICs müssen in alle Dies TSVs eingebracht werden. Dadurch ist die Wiederverwendung existierender Entwürfe nicht ohne Überarbeitung möglich. Im Idealfall werden alle einzelnen ICs gemeinsam entworfen. Gelingt es, miteinander verschaltete Baugruppen in der Nachbarschaft auf horizontaler oder vertikaler Ebene zu platzieren, können Signalwege deutlich verkürzt und damit Taktraten und Performanz gesteigert werden. Diese technisch anspruchsvollste Art der 3D-Integration befindet sich heute noch im Entwicklungsstadium.

Eine Alternative zum direkten Stapeln ist das Einfügen eines *Interposers*, die eine Zwischenschicht zur Verbindungsrealisierung darstellt. Über seine zwei bis vier Verdrahtungsebenen und TSVs können die Verbindungen zwischen verschiedenen Dies hergestellt und, wenn nötig, umgeordnet werden. Er besteht aus einem gedünnten Silizium Die und enthält in der Regel keine aktiven Bauelemente. Im Vergleich zur Leiterplatte oder dem SiP sind die Verdrahtungsstrukturen wesentlich feiner. Dadurch können das resultierende System sehr kompakt aufgebaut und kurze Leitungslängen erreicht werden. Abbildung 2.4b zeigt eine Aufbauvariante, bei der zwei Dies in Flip-Chip-Technik mit Mikroballs auf dem Interposer montiert werden. Eine Montage mit Kleben und Bonden wäre ebenso denkbar.

**Abb. 2.4** Aufbauvarianten mehrerer ICs (Dies) ohne und mit Interposer, **a** Stapel ohne Interposer, **b** Stapel mit Interposer, **c** Nebeneinander auf Interposer

Da in die Dies keine TSVs eingebracht werden müssen, ist die Wiederverwendung existierender ICs möglich. In bestimmten Fällen kann es sinnvoll sein, ICs nebeneinander auf einem Interposer zu platzieren (Abb. 2.4c), was man oft als 2.5D-Integration bezeichnet.

Auf den ersten Blick erscheint die interposerbasierte Systemintegration einfach realisierbar zu sein. Beim Entwurf eines Interposers stoßen aktuelle Werkzeuge aufgrund seiner Verdrahtungsdichte und der wenigen zur Verfügung stehenden Metallebenen an ihre Grenzen. Eine besondere Herausforderung stellt die Gewährleistung der Signalintegrität und die Stabilität von Betriebsspannungs- und Masseanschlüssen dar.

#### 2.3 Beispiele für 3D-integrierte Systeme

Die Entscheidung für eine bestimmte 3D-Integrationstechnik wird vom Einsatzgebiet, den daraus resultierenden Anforderungen und den zu erwartenden Stückzahlen bestimmt. Im Folgenden werden erfolgreiche Beispiele von 3D-integrierten Systemen vorgestellt.

#### 2.3.1 System-In-Package für Medizintechnik

Innerhalb eines Forschungsprojekts Dionysys [RKJ09] wurde der in Abb. 2.5 gezeigte Prototyp [WES10] eines Elektrokardiogrammgerätes als SiP entwickelt. Auf dem  $2,4 \times 2,4$  cm<sup>2</sup> großen Substrat sind folgende Teilsysteme aufgebaut:

- drei empfindliche Eingangsverstärker zur Aufbereitung der EKG-Eingangssignale, davon zwei gestapelt, der dritte wurde über dem Dezimator montiert,

- · ein Dezimator zur Digitalisierung,

- ein Mikrocontroller zur Signalverarbeitung und Steuerung,

- ein IEEE 802.15.4 Funkmodul, das im 2.4 GHz ISM-Band sendet,

- ein Oszillator zur Takterzeugung sowie weitere passive Bauelemente.

Während die Eingangsverstärker und der Dezimator speziell entwickelte ICs sind, wurden für Mikrocontroller und Funkmodul Standardschaltkreise in ungehäuster Version (bare die) eingesetzt.